기술이전 상세 정보를 불러오는 중입니다...

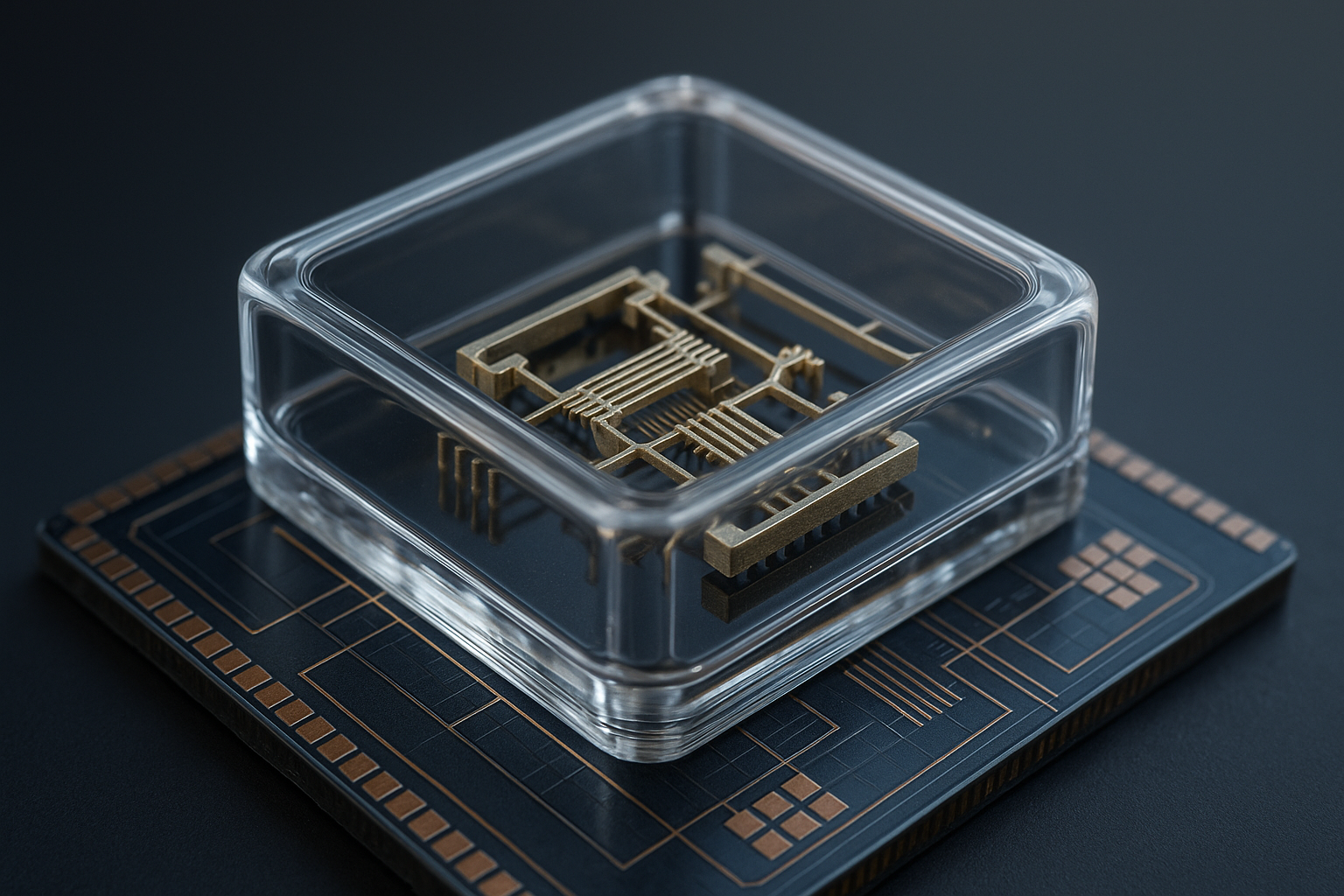

기존 전기기계 소자 패키징은 칩 면적 감소에 따른 성능 저하와 금속 배선층 손상으로 인한 구조적 불안정성 문제를 겪고 있습니다. 본 기술은 이러한 한계를 극복하기 위해 고집적 3차원 집적이 가능한 전기기계 소자 패키지 및 그 제조 방법을 제안합니다. 특히, 금속 배선층에 영향을 주지 않으면서 활성 영역을 진공 패키징하며, TEOS 기반으로 CMOS 공정 호환성을 극대화합니다. 또한, 낮은 금속 배선층으로도 높은 집적도를 구현하고 기존 CMOS 공정을 활용하여 저비용으로 제조 가능합니다. 이 기술은 구조적으로 안정된 CMOS-NEM 재구성 로직을 구현하며, 외부 환경으로부터 소자를 보호하는 진공 패키징을 통해 뛰어난 내구성을 제공합니다. 이를 통해 저전력, 고집적, 고성능의 반도체 소자 개발에 크게 기여할 수 있습니다.

| 기술명 | |

| 전기기계 소자 패키지 및 이의 제조 방법 | |

| 기관명 | |

| 서강대학교산학협력단 | |

| 대표 연구자 | 공동연구자 |

| 최우영 | - |

| 출원번호 | 등록번호 |

| 1020170144644 | 1019908060000 |

| 권리구분 | 출원일 |

| 특허 | 2017.11.01 |

| 중요 키워드 | |

MEMS 기술희생층 공정반도체 패키징패키징 솔루션삼차원 집적 기술TEOS 기반2.5D 패키징NEMS 기술전기기계 소자 패키지CMOS 공정 호환CMOS-NEM재구성 로직고집적 반도체진공 패키징저비용 제조전자부품 | |

기술이전 상담신청

연구자 미팅

기술이전 유형결정

계약서 작성 및 검토

계약 및 기술료 입금

보유 기술 로딩 중...

인기 게시물 로딩 중...